## InterPort<sup>™</sup> LAG software module

The InterPort™ Link Aggregation (LAG) software module is a portable implementation of all management and control plane components of IEEE 802.1AX-2008. The standard describes using multiple Ethernet ports in parallel to increase the link speed beyond the limits of any one single port and to increase the redundancy for higher availability. The LAG software module also provides a full implementation of the Link Aggregation Control Protocol (LACP) to allow automatic configuration of aggregation groups and faster switchovers in the event of changes in link connectivity.

Link Aggregation allows one or more links to be aggregated together to form a Link Aggregation Group, such that a MAC Client can treat the Link Aggregation Group as a single link. The aggregated group consists of one or several parallel instances of full duplex point-to-point links operating at the same data rate. The standard compliant, pre-tested and field proven InterPort LAG software module enables networking equipment providers to rapidly and cost-effectively offer carrier-grade features on their next-generation Ethernet, broadband access and wireless product lines.

#### features

The Kuatro Technologies InterPort LAG Software Module includes a complete set of Application Programming Interfaces (APIs) to implement control plane components as defined by the IEEE 802.3ad-2004 standard and as updated by IEEE 802.1AX-2008. The LAG module also supports MEF 20 and MEF 22.1 requirements, as well as providing support for stateless High Availability.

| Feature                                                   | InterPort™<br>LAG Software |

|-----------------------------------------------------------|----------------------------|

| Support LACP                                              | Yes                        |

| Support Coupled control MUX state machine                 | Yes                        |

| Support Independent control MUX state machine             | Yes                        |

| Support explicit aggregation of links                     | Yes                        |

| Support dynamic aggregation of links                      | Yes                        |

| Churn detection                                           | Yes                        |

| Aggregation Port Debug Information support                | Yes                        |

| Support independent Distribution Algorithm per Aggregator | Yes                        |

| Backwards compatibility with aggregation-unaware devices  | Yes                        |

| Dual Stateless Mode High Availability                     | Yes                        |

#### benefits

- > Up to 50% time to market reduction

- 25 to 35% savings in development costs

- > Pre-tested software modules minimize project risks

- Integrated solution delivery by Kuatro's R&D design services

- Portable to any OS and hardware platform

- > Accelerates failure recovery

### architecture

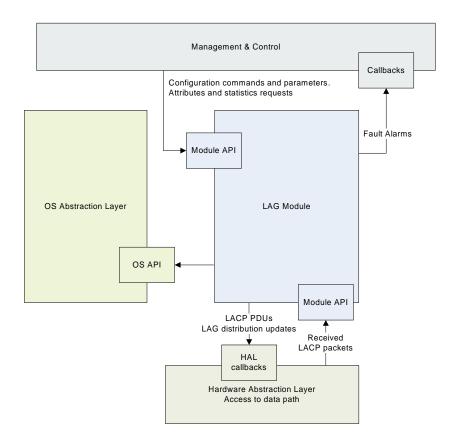

InterPort LAG has well defined interfaces including OS abstraction APIs, Hardware Abstraction Layer (HAL) callbacks and APIs to management and control layer software. These APIs enable portability to various platforms using different operating systems and different data plane designs whether FPGA, network processor, Ethernet silicon or virtualized platform based.

# supported standards

- > Ethernet Link

Aggregation IEEE 802.3ad

2004 as updated by

IEEE 802.1AX-2008

- Supports MEF 20 and MEF 22.1 requirements

#### contact us

E: <a href="mailto:info@kuatrotech.com">info@kuatrotech.com</a>

W: <a href="mailto:www.kuatrotech.com">www.kuatrotech.com</a>